ข่าว

DAC สำรวจบทบาทของ AI และ ML ในตลาด

Moscone Center, San Francisco จะเป็นเจ้าภาพ DAC 25-28 มิถุนายน

OneSpin Solutions และ ระบบออกแบบ Austemper ทั้งสองจะเน้นเครื่องมือสำหรับการตรวจสอบความปลอดภัยในการทำงาน Austemper จะมุ่งเน้นไปที่การพัฒนาระบบภารกิจที่สำคัญโดยใช้ชุดเครื่องมือ KaleidoScope ซึ่งสนับสนุนการออกแบบอนาล็อกสำหรับการแพร่กระจายความผิดพลาดแบบผสมสัญญาณ ชุดเครื่องมืออัตโนมัติมีการวิเคราะห์ความปลอดภัยการสังเคราะห์และการตรวจสอบความปลอดภัยสำหรับแอพพลิเคชันที่มุ่งเน้นการรับรอง ใช้สำหรับการออกแบบยานยนต์ขนาดใหญ่ใน ADAS และการขับขี่แบบอิสระ การจำลองความผิดพลาดพร้อมกันรวมถึงการจำลองตามคำแนะนำของ ISO 26262 เพื่อให้สอดคล้องกับข้อกำหนดของ ASIL

เมื่อเร็ว ๆ นี้ บริษัท ได้ร่วมมือกับ OneSpin Solutions เพื่อนำมาใช้เป็นเครื่องมือสำหรับการใช้งานด้านความปลอดภัยซึ่งรวมการออกแบบและการตรวจสอบการไหลซึ่งจะแสดงให้เห็นที่บูธ OneSpin กลไกด้านความปลอดภัยของฮาร์ดแวร์ถูกใส่เข้าไปในการออกแบบชิปและเครื่องมือ OneSpin Solutions จะตรวจสอบตรรกะด้านความปลอดภัยของฮาร์ดแวร์อย่างเป็นทางการ การตรวจสอบความเท่าเทียมกันจะช่วยให้แน่ใจได้ว่าตรรกะด้านความปลอดภัยที่แทรกไม่มีผลต่อการทำงานปกติและการวิเคราะห์การตรวจจับข้อผิดพลาดจะตรวจสอบว่ากลไกด้านความปลอดภัยทำงานได้อย่างถูกต้องในกรณีที่มีข้อผิดพลาดแบบสุ่ม

นอกจากนี้ OneSpin ยังมีการส่งเสริมชุดเครื่องมือวัดผลการทำงานของเครื่องมือตามการตรวจสอบจากTÜVSÜDเกี่ยวกับกระบวนการพัฒนาเครื่องมือของตน ชุดเริ่มต้นมีให้สำหรับเครื่องมือ 360 EC-FPGA EDA ของ บริษัท ซึ่งเป็นการตรวจสอบความเท่าเทียมกันตามลำดับอัตโนมัติเพื่อป้องกันไม่ให้กระแสการออกแบบของ FPGA มีข้อผิดพลาดในการนำไปปฏิบัติ ชุดได้รับการรับรองมาตรฐาน ISO 26262, IEC 61508 และ EN 50128

ข้อมูลเชิงลึกของ FPGA

ยังคงมีการออกแบบ FPGA, Plunify ได้ร่วมมือกับ Xilinx เพื่อเสนอชุดการออกแบบ Vivado ในระบบคลาวด์โดยใช้แพลตฟอร์ม Plunify Cloud นักออกแบบต้องจ่ายเงินเพียง 50C เพื่อรวบรวมโครงการ Vivado ในเมฆ Amazon Web Services (AWS) รวมถึงใบอนุญาต

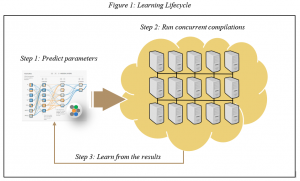

นอกจากนี้ บริษัท ยังจะแสดงให้เห็นถึงการปรับปรุงซอฟท์แวร์ InTime timing closure เพื่อเพิ่มประสิทธิภาพของเวลา FPGA ในระบบคลาวด์ (รูปที่ 1) InTime Optimization Methodology สามารถปรับปรุงความถี่นาฬิกาได้ถึง 20-80% และตอบสนองความต้องการด้านเวลาในหลายวันแทนที่จะเป็นสัปดาห์ผ่านการเรียนรู้ด้วยเครื่อง ซอฟต์แวร์นี้ยังเร่งการปิดบัญชีและการเพิ่มประสิทธิภาพของเวลาและเข้าถึงได้ผ่านทางระบบคลาวด์

นอกจากนี้ บริษัท ยังจะแสดงให้เห็นถึงการปรับปรุงซอฟท์แวร์ InTime timing closure เพื่อเพิ่มประสิทธิภาพของเวลา FPGA ในระบบคลาวด์ (รูปที่ 1) InTime Optimization Methodology สามารถปรับปรุงความถี่นาฬิกาได้ถึง 20-80% และตอบสนองความต้องการด้านเวลาในหลายวันแทนที่จะเป็นสัปดาห์ผ่านการเรียนรู้ด้วยเครื่อง ซอฟต์แวร์นี้ยังเร่งการปิดบัญชีและการเพิ่มประสิทธิภาพของเวลาและเข้าถึงได้ผ่านทางระบบคลาวด์

การส่งเสริมเทคโนโลยี eFPGA, Achronix Semiconductor กำลังทำงานร่วมกับผู้เชี่ยวชาญด้าน IP CAST เพื่อเพิ่ม throughput และทำให้ประหยัดในการจัดเก็บหน่วยความจำ

ผู้เข้าร่วมงานทั้งสองรายจะอธิบายว่าการบีบอัดข้อมูลแบบ lossless ของ CAST ได้รับการปรับเปลี่ยนไปเป็นพอร์ตโฟลิโอ Achronix FPGA เพื่อใช้ในศูนย์ข้อมูลและแอพพลิเคชั่นการโอนย้ายข้อมูลบนมือถือ การใช้ฮาร์ดแวร์ของการบีบอัดข้อมูลแบบ lossless สำหรับ Deflate, GZIP และ ZLIB สามารถทำงานร่วมกับการใช้งานซอฟต์แวร์ที่ใช้สำหรับการบีบอัดหรือบีบอัดเพื่อให้สามารถรับส่งข้อมูลได้ถึง 100Gbit / s โดยมีการบีบอัดต่ำและแฝงต่ำควบคู่ไปกับเทคโนโลยี Speedcore eFPGA เพื่อเคลื่อนย้ายและจัดเก็บข้อมูลขนาดใหญ่ ข้อมูลที่ใช้พลังงานต่ำ

CAST ได้ย้าย IP ไปใช้ FPGA ของ Achronix แล้ว

ประสิทธิภาพการใช้พลังงาน

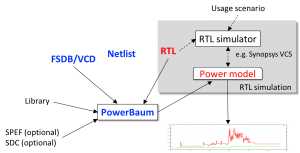

การพูดเกี่ยวกับการจัดการพลังงาน, ผู้เข้าร่วมงานคนอื่น, Baum, ระบุประสิทธิภาพการใช้พลังงานเป็นพื้นที่ส่วนใหญ่ภายใต้การพัฒนาในการออกแบบชิป เครื่องมือวิเคราะห์และจำลองแบบอัตโนมัติของเครื่องนี้ได้รับการออกแบบมาสำหรับโครงการด้านยานยนต์, IOT, โทรศัพท์มือถือระบบเครือข่ายและเซิร์ฟเวอร์ PowerBaum 2.0 (รูปที่ 3) สนับสนุนพลังงานแบบไดนามิกและแบบสถิตโดยใช้คำอธิบาย RTL และ netlist และเพิ่มการสนับสนุนสำหรับการวิเคราะห์พลังงานด้วยการจำลองฮาร์ดแวร์ นี้กล่าวว่า บริษัท ช่วยให้วิศวกรในการแก้ไขปัญหาข้อบกพร่องด้านพลังงานในสถานการณ์ซอฟต์แวร์ที่สมจริง เครื่องมือนี้ยังสนับสนุนการวิเคราะห์ด้วยอุณหภูมิโดยพลการซึ่งระบุโดยนักออกแบบเพื่อประเมินผลกระทบของอุณหภูมิต่อการใช้พลังงานของการออกแบบ

ที่ DAC บริษัท ยังจะแนะนำ PowerWurzel ซึ่งเป็นเครื่องมือวิเคราะห์ระดับประตูซึ่งจะรวมเข้ากับ PowerBaum สำหรับการสร้างแบบจำลองทางไฟฟ้า

รูปที่ 3 เครื่องมือของ Baum วิเคราะห์ประสิทธิภาพการใช้พลังงาน

เครื่องมือออกแบบและตรวจสอบ SoC ที่ใช้ระบบ Cloud สำหรับการออกแบบ IC จาก ตัวชี้วัด รวม Cloud Simulator และ Verification Manager ซึ่งออกแบบมาเพื่อจัดการกับความต้องการในการจำลองและทรัพยากรปรับค่าขึ้นหรือลงทุกๆนาที บริษัท อ้างว่า Google Cloud มีขีดความสามารถในการจำลองแบบ SystemVerilog และระบบการตรวจสอบแบบเดิมบนเว็บเพื่อการถดถอยครั้งที่รวดเร็วลดข้อผิดพลาดของรหัสลำต้นและความครอบคลุมของโค้ดที่คาดการณ์ได้

นอกเหนือจากผู้เข้าร่วมงานแล้วงานนี้ยังเป็นเจ้าภาพการประชุมด้านเทคนิคและโปรแกรมการกล่าวสุนทรพจน์ในประเด็นเฉพาะ ในปีนี้ Cadence จะเป็นเจ้าภาพการสอนเกี่ยวกับ "ความปลอดภัยในการใช้งานและความน่าเชื่อถือสำหรับแอพพลิเคชันยานยนต์" และอีกทางหนึ่งคือการเรียนรู้ด้วยเครื่อง (Machine Learning จะนำการรู้จำคำพูดไปสู่ระดับถัดไป) ปาฏิหาริย์โดย Anna-Katrina Shedletsky, Instrumental ในวันจันทร์ที่ 25 มิถุนายนจะเน้นเรื่อง 'Automating Intelligence: Machine Learning และ Future of Manufacturing' การใช้ ML และ AI สำหรับหุ่นยนต์อำนวยความช่วยเหลือทางสังคม (SAR) ได้รับการสำรวจในปาฐกถาพิเศษของพฤหัสบดีโดย Maja Matarićมหาวิทยาลัยเซาเทิร์นแคลิฟอร์เนียที่จะนำเสนอ 'Automation and Augmentation: หุ่นยนต์ช่วยผู้ช่วยและอนาคตของการทำงาน'

ประเด็นสำคัญอื่น ๆ สนับสนุน RISC-V เป็นวิธีการสร้างสถาปนิกอิสระจากสถาปัตยกรรมชุดคำสั่งที่เป็นกรรมสิทธิ์ (ISA) David A Patterson, Google และ University of California จะนำเสนอ "ยุคใหม่สำหรับสถาปัตยกรรมคอมพิวเตอร์: ตัวเร่งการทำงานเฉพาะโดเมนและเปิด RISC-V"

พื้นที่ใหม่ในปีนี้ที่ DAC คือ Alley Design Infrastructure ความคิดริเริ่มโดย ESD Alliance และสมาคม สำหรับผู้เชี่ยวชาญด้านคอมพิวเตอร์ประสิทธิภาพสูง เป็นพื้นที่ที่ทุ่มเทให้กับโครงสร้างพื้นฐานด้านไอทีสำหรับการออกแบบระบบและส่วนประกอบอิเล็กทรอนิกส์ รวมทั้งความต้องการด้านคอมพิวเตอร์และการจัดเก็บข้อมูลสำหรับการออกแบบและการจัดการการใช้งานระบบคลาวด์มีโรงละครศาลาด้านการออกแบบบนเมฆที่ออกแบบมาเพื่อการจัดการใบอนุญาตการประมวลผลแบบตารางและความปลอดภัยของข้อมูล