### MAX32630 ERRATA SHEET

#### **Revision A1 Errata**

The errata listed below describe situations where components of this revision perform differently than expected or differently than described in the data sheet. Maxim Integrated Products, Inc., intends to correct these errata when the opportunity to redesign the product presents itself.

This errata sheet only applies to components of this revision. These components are branded on the topside of the package with a six-digit code in the form yywwRR, where yy and ww are two-digit numbers representing the year and work week of manufacture, respectively, and RR is the revision of the component. To obtain an errata sheet on other die revisions, visit the Maxim website at www.maximintegrated.com/errata.

#### 1) GPIO DRAWS EXCESSIVE CURRENT IF VIH EXCEEDS SELECTED GPIO SUPPLY

#### **Description:**

When V<sub>IH</sub> of a GPIO pin exceeds the selected GPIO supply (V<sub>DDIO</sub> or V<sub>DDIOH</sub>), the GPIO draws excessive current.

#### Workaround:

Ensure  $V_{IH} \le$  is selected supply. Alternatively, configure GPIO mode 6 (TS\_SLOW) when the pin is under firmware control, GPIO mode 15 is the default.

#### 2) VOH DOES NOT OBSERVE SPECIFICATION IF VDDB > 0V

#### **Description:**

VOH(MIN)specification is not met if the USB peripheral is externally powered from the VDDB pin.

#### Workaround:

None. VOH can decrease approximately 70mV when the USB is powered from the VDDB pin.

#### 3) IDD12 FLP0 AND IDD12 FLP1 DO NOT OBSERVE SPECIFICATION

#### **Description:**

Current consumption in LP0 and LP1 modes is higher than the specified value.

#### Workaround:

This issue is addressed in the latest version of the SDK/API. Using the supplied drivers limits it IDD12 to approximately IDD12\_FLP3 in modes LP0 and LP1.

### 4) PMU WRITE DESCRIPTOR MASK DOES NOT OPERATE AS EXPECTED

#### **Description:**

The PMU descriptor mask is expected to operate as:

(NEW\_VALUE & MASK) | (ORIG\_DATA & ~MASK)

but operates as:

NEW DATA | (ORIG DATA & ~MASK).

#### Workaround:

AND NEW\_VALUE with MASK before writing to the WrData register.

#### 5) PMU ONLY SUPPORTS CHANNELS 0-4

#### **Description:**

PMU channel 5 does not operate as intended. With the provided workaround, PMU channels 0–4 are available.

#### Workaround:

The workaround consists of three steps:

- 1. Set clock gating to ALWAYS-ON. This software workaround is implemented in the latest version of the SDK/API. No workaround for this step is necessary if the supplied drivers are used.

- 2. One of PMU channel 5 must be set in a loop, jumping back to itself. This software workaround is implemented in the latest version of the SDK/API. No workaround for this step is necessary if the supplied drivers are used.

- 3. MOVE and TRANSFER commands must have the STOP bit set.

# 6) USB HARDWARE CANNOT DETECT SUBSEQUENT SUSPEND EVENTS AFTER INITIAL SUSPEND/RESUME CYCLE

#### **Description:**

After a USB bus reset, the USB peripheral properly detects only the first USB bus suspend condition. Subsequent suspend conditions are not detected until a bus reset occurs.

#### Workaround:

Upon detection of resume signaling from the host, set the SIGRWU bit to cause a remote wakeup. Signaling for a remote wakeup is the same bus state as resume, but is shorter in duration. Therefore, this remote wakeup is benign and is not seen by the host. The remote wakeup should only be issued upon detection of resume signaling. If the bus activity is a bus reset, the remote wakeup should not be issued.

This workaround resolves the issue, and the device again can detect a suspend condition. Example software is available that implements this workaround.

#### 7) GPIO STATE NOT MAINTAINED IN LP0 OR LP1 MODES

#### **Description:**

The hardware that automatically maintains the state of GPIO pins in the LP0 or LP1 modes does not work as intended.

#### Workaround:

Disable the "GPIO freeze" feature that automatically maintains the GPIO state in LP0 and LP1 modes. Explicitly enable the GPIO freeze feature in software before entering the LP0 or LP1 modes. Explicitly disable the GPIO freeze feature in software immediately after exiting the LP0 or LP1 modes.

**Note:** This software workaround is implemented in the latest version of the MAX32620 SDK/API. No workaround is necessary if the supplied drivers are used.

#### 8) FLASH MEMORY PAGE PROTECTION FEATURE DOES NOT OPERATE AS EXPECTED

#### **Description:**

The flash memory page protection control registers do not operate as expected.

#### Workaround:

None. Do not modify the page protection control registers from their default state.

#### 9) SPI MASTER DOES NOT OPERATE AS EXPECTED IN MODE 1, 2, OR 3

#### **Description:**

The SPI master does not operate as intended in mode 1, 2, or 3.

#### Workaround:

None.

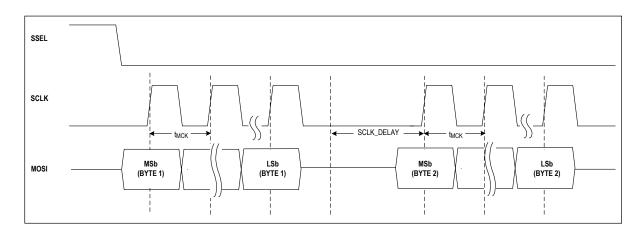

#### 10) SPI MASTER INTERBYTE DELAY IN MODE 0

#### **Description:**

The SPI master remains low one or more SCLK cycles after transmitting 8 bits of data, resulting in an interbyte delay when transmitting back-to-back bytes. This erratum does not affect the integrity of the synchronous SPI bus because no data is clocked in or out by the SPI slave during the delay time SCLK is asserted low.

In single mode, the delay occurs after SDIO[0] has transmitted all eight bits.

In dual mode, the delay occurs after SDIO[1:0] have each transmitted four bits.

In quad mode, the delay occurs after SDIO[3:0] have each transmitted two bits.

The length of the delay is a function of the SPI clock frequency as shown in the following table. The SPI master must be operated in sample mode with a maximum frequency of 24MHz.

| SCLK OUTPUT FREQUENCY (f <sub>MCK</sub> ) | SCLK_DELAY                                |  |  |

|-------------------------------------------|-------------------------------------------|--|--|

| SPIM peripheral clock/2                   | 2 x t <sub>(SPI</sub> peripheral clock)   |  |  |

| SPIM peripheral clock/4                   | 3 x t(SPI peripheral clock)               |  |  |

| SPIM peripheral clock/8                   | 5 x t <sub>(SPI</sub> peripheral clock)   |  |  |

| SPIM peripheral clock/16                  | 9 x t <sub>(SPI</sub> peripheral clock)   |  |  |

| SPIM peripheral clock/32                  | 17 x t <sub>(SPI</sub> peripheral clock)  |  |  |

| SPIM peripheral clock/64                  | 33 x t <sub>(SPI</sub> peripheral clock)  |  |  |

| SPIM peripheral clock/128                 | 65 x t <sub>(SPI</sub> peripheral clock)  |  |  |

| SPIM peripheral clock/256                 | 129 x t <sub>(SPI peripheral clock)</sub> |  |  |

#### Workaround:

None.

#### 11) SPI SLAVE DOES NOT OPERATE AS EXPECTED

#### Description:

The SPI master does not operate as intended.

#### Workaround:

None. Do not use any instance of the SPI slave peripheral.

#### 12) P1.6 DOES NOT OPERATE AS EXPECTED WHEN 32kHz OUTPUT MODE ON P1.7 IS ENABLED

#### **Description:**

Enabling the 32kHz clock output mode on P1.7 configures P1.6 as an input with an internal pullup. The primary and secondary functions, pulse train output, and timer input as unavailable in this configuration. P1.6 remains in this state until the 32kHz clock output mode on P1.7 is disabled. The internal pullup configuration increases power consumption in low power modes.

#### Workaround:

Do not use P1.6 except as a GPIO input while the 32kHz clock output mode is enabled.

#### 13) READS OF IOMAN\_SPIM2\_REQ[31:16] RETURN IOMAN\_SPIM2\_REQ[30:15]

#### **Description:**

Reads of IOMAN\_SPIM2\_REQ[31:16] instead return IOMAN\_SPIM2\_REQ[30:15]. As a result, the acknowledge bits in IOMAN\_SPIM2\_ACK[31:16] do not align with the request bits in IOMAN\_SPIM2\_REQ[31:16].

#### Workaround:

To read the correct value for IOMAN\_SPIM2\_REQ[31:16], implement the following (pseudocode) procedure:

scratch = IOMAN SPIM2 REQ & 0x7FFF8000/mask off all bits except 30:15

scratch = (scratch << 1) // scratch now contains the correct values in bits 31:16

# 14) GPIO\_FREE\_P1.[7:6] ARE INCORRECT WHEN 32kHz OUTPUT MODE ON P1.7 IS ENABLED

#### **Description:**

When the 32kHz output mode on P1.7 is enabled, GPIO\_FREE\_P1.7 GPIO = 1 and GPIO\_FREE\_P1.6 = 0. Instead, the bits should be GPIO\_FREE\_P1.7 GPIO = 0 and GPIO\_FREE\_P1.6 = 1.

#### Workaround:

Software should recognize the bits are inverted when reading GPIO\_FREE\_P1.[7:6].

## **Revision History**

| REVISION | REVISION | DESCRIPTION     | PAGES   |

|----------|----------|-----------------|---------|

| NUMBER   | DATE     |                 | CHANGED |

| 0        | 8/16     | Initial release | _       |

© 2016 Maxim Integrated Products, Inc. All rights reserved. The Maxim logo and Maxim Integrated are trademarks of Maxim Integrated Products, Inc. in the United States and other jurisdictions throughout the world.