# 8-bit CID MICROCONTROLLER

### Table of Contents-

| 1. | GENE   | RAL DESCRIPTION                                        | 2    |

|----|--------|--------------------------------------------------------|------|

| 2. | FEATU  | JRES                                                   | 2    |

| 3. | PIN CO | DNFIGURATION                                           | 4    |

| 4. | PIN DE | ESCRIPTION                                             | 5    |

| 5. | BLOC   | CDIAGRAM                                               | 7    |

| 6. | FUNC   | FIONAL DESCRIPTION                                     | 8    |

|    | 6.1    | Memory Organization                                    | 9    |

|    | 6.2    | Special Function Registers                             | . 12 |

|    | 6.3    | Initial State of Registers                             | . 32 |

|    | 6.4    | Instruction                                            | 33   |

|    | 6.5    | Power Management                                       | . 37 |

|    | 6.6    | Reset                                                  | 38   |

|    | 6.7    | Interrupt                                              | 38   |

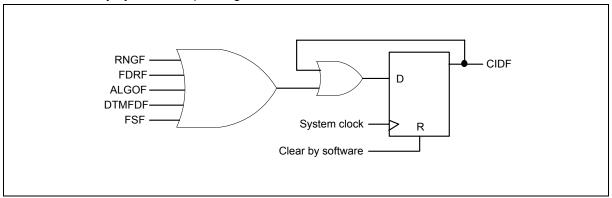

|    | 6.8    | Programmable Timers/Counters                           | 41   |

|    | 6.9    | Serial Port 1                                          | 45   |

|    | 6.10   | Comparator                                             | 47   |

|    | 6.11   | DTMF Generator                                         | 47   |

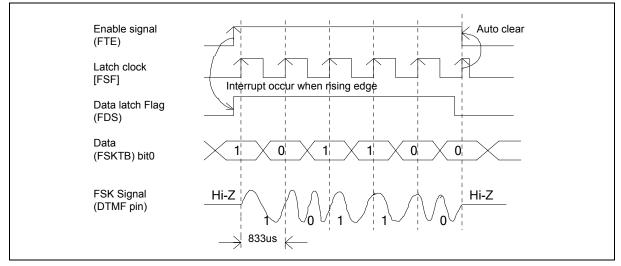

|    | 6.12   | FSK Generator                                          | 48   |

|    | 6.13   | I/O Ports                                              | 49   |

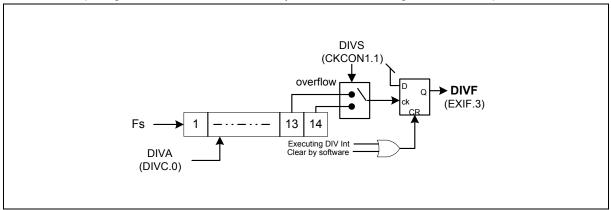

|    | 6.14   | Divider                                                | 50   |

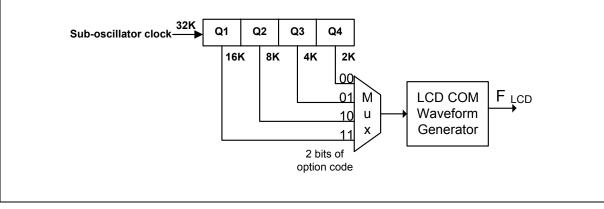

|    | 6.15   | LCD                                                    | 51   |

|    | 6.16   | Calling Identity Delivery (CID)                        | 54   |

| 7. | ELECT  | RICAL CHARACTERISTICS                                  | . 68 |

|    | 7.1    | Maximum Ratings*                                       | . 68 |

|    | 7.2    | Recommended Operating Conditions                       | 68   |

|    | 7.3    | DC Characteristics                                     | 69   |

|    | 7.4    | Electrical Characteristics – Gain Control OP-Amplifier | 70   |

|    | 7.5    | AC Characteristics                                     | 71   |

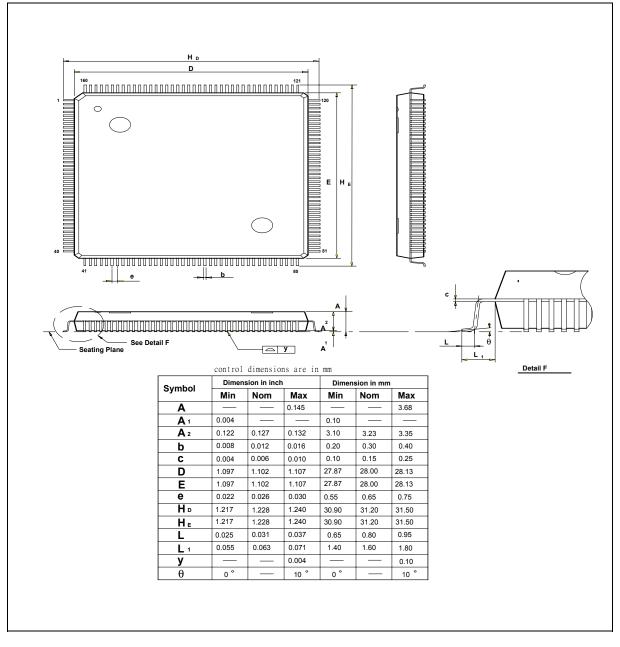

| 8. | PACKA  | AGE                                                    | 74   |

| 9. | REVIS  | ION HISTORY                                            | 75   |

### 1. GENERAL DESCRIPTION

The W925E/C625 is an all in one single 8-bit micro-controller with widely used Calling Identity Delivery (CID) function. The 8-bit CPU core is based on the 8051 family; therefore, all the instructions are compatible to the Turbo 8051 series. The CID part consisted of FSK decoder, DTMF receiver, CPE\* Alert Signal (CAS) detector and Ring detector. Also built-in DTMF generator and FSK generator with baud rate 1200 bps (bits/sec). Using W925E/C625 can easily implement the CID adjunct box and the feature phone or Short Message Service (SMS) phone with CID function. The main features are listed in the next section.

### 2. FEATURES

- **APPLICATION**: The **SMS** phone with CID function and CID adjunct box.

- **CPU**: 8-bit micro-controller is similar to the 8051 family.

- EEPROM type operating voltage:

$\mu$ C: Depend on the operating vol. option. Either 2.4 to 3.6V or 3.0 to 5.5V for operating. If 2.4 to 3.6V be selected, the  $\mu$ C operating range is from 2.4 to 3.6V, else if 3.0 to 5.5V be selected, the  $\mu$ C operating range is from 3.0 to 5.5V.

CID: 3.0 to 5.5V.

- MASK type operating voltage:

μC: 2.2 to 5.5V.

CID: 3.0 to 5.5V.

- Dual-clock operation:

- Main oscillator: 3.58MHz crystal for CID and DTMF function. And built-in RC oscillator.

- Sub oscillator: 32768Hz crystal.

- Main and sub oscillators are enable/disable by bit control individually.

- **ROM**: 64K bytes internal flash EEPROM/MASK ROM type.

- Up 64K bytes for program ROM.

- Total 64K bytes for look-up table ROM.

- · RAM:

- 256 bytes on chip scratch-pad RAM.

- 4K bytes on chip RAM for MOVX instruction.

- 224 bytes on chip LCD RAM.

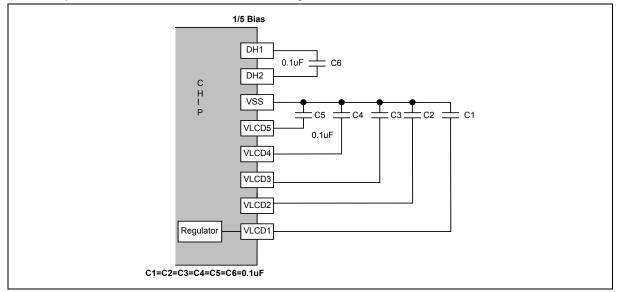

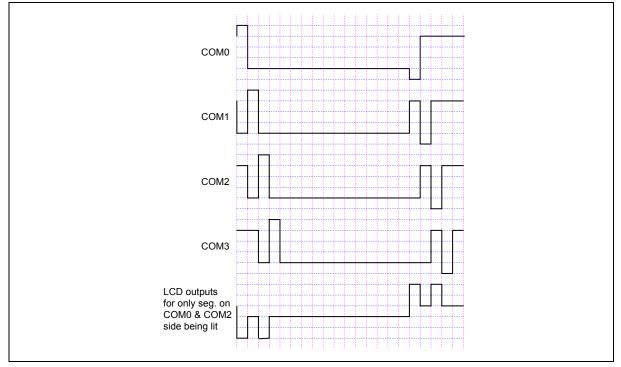

- LCD: dot matrix control method.

- 1792 dots: 56 Segments x 32 Common, 1/5 bias.

- · CID:

- Compatible with Bellcore TR-NWT-000030 & SR-TSV-002476, British Telecom(BT) SIN227, U.K. Cable Communication Association(CCA) specification.

- FSK modulator/demodulator: for Bell 202 and ITU-T V.23 FSK with 1200-baud rate.

- CAS detector: for dual tones of Bellcore CAS and BT Idle State and Loop State Dual Tone Alert Signal (DTAS).

- DTMF generator/receiver;

- Ring detector: for line reversal for BT, ring burst for CCA or ring signal for Bellcore.

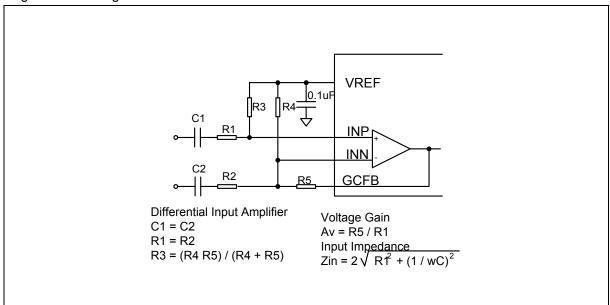

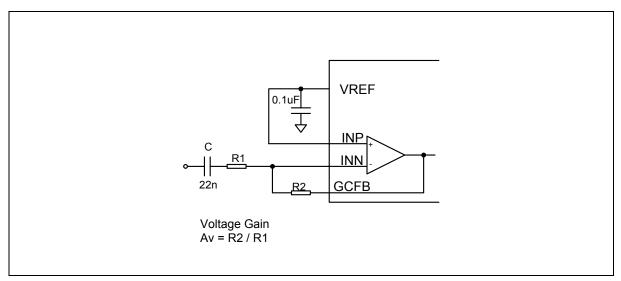

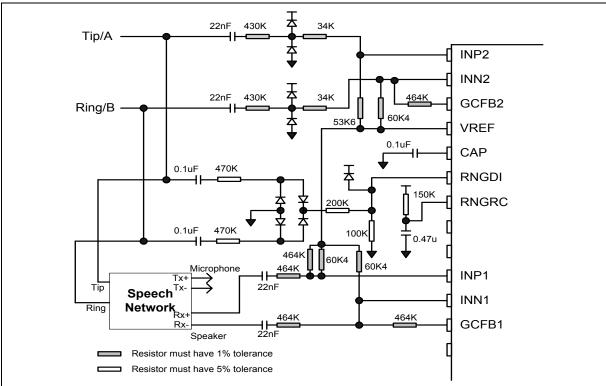

- Two independent OP amps with adjustable gain for Tip/Ring and Telephone Hybrid connections.

- I/O: 40 I/O pins.

- P0: Bit and byte addressable. I/O mode can be bit controlled. Open drain type.

- P1~P3: Bit and byte addressable. Pull high and I/O mode can be bit controlled.

- P4 : Byte addressable. Pull high and I/O mode can be bit controlled.

Note: "CPE\*" Customer Premises Equipment

- Power mode:

- Normal mode: Normal operation

- **Dual-clock slow operation mode**: System is operated by the sub-oscillator (Fosc=Fs and Fm is stopped)

- **Idle mode**: CPU hold. The clock to the CPU is halted, but the interrupt, timer and watchdog timer block work normally but CID function is disabled.

- **Power down mode**: All activity is completely stopped and power consumption is less than 1  $\mu$ A.

- Timer: 2 13/16-bit timers, or 8-bit auto-reload timers, that are Timer0 and Timer1.

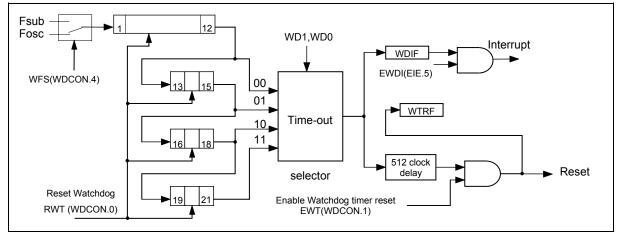

- Watchdog timer: WDT can be programmed by the user to serve as a system monitor.

- Interrupt: 11 interrupt sources with two levels of priority.

- 4 interrupts from INT0, INT1, INT2 and INT3.

- 2 interrupts from Timer0, Timer1.

- 1 interrupt from Serial port.

- 1 interrupt from CID.

- 1 interrupt from 13/14-bit Divider.

- 1 interrupt from Comparator.

- 1 interrupt from Watch Dog Timer.

- **Divider:** 13/14 bit divider, clock source from sub-oscillator, therefore, DIVF set every 0.25/0.5 Sec.

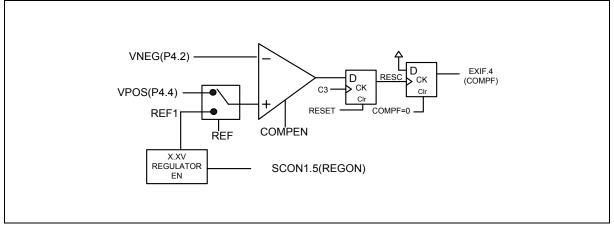

- Comparator:

- Comparator:1 analog input from VNEG pin, 2 reference input pins, one is from VPOS pin and another is from internal 1.0v regulator output.

- Serial port:

- An 8-bit serial transceiver with SCLK and SDATA.

- Package:

- 160pin QFP : The part numbers are W925E625 & W925C625

- Lead free 160pin QFP: The part numbers are W925E625FG & W925G625

### 3. PIN CONFIGURATION

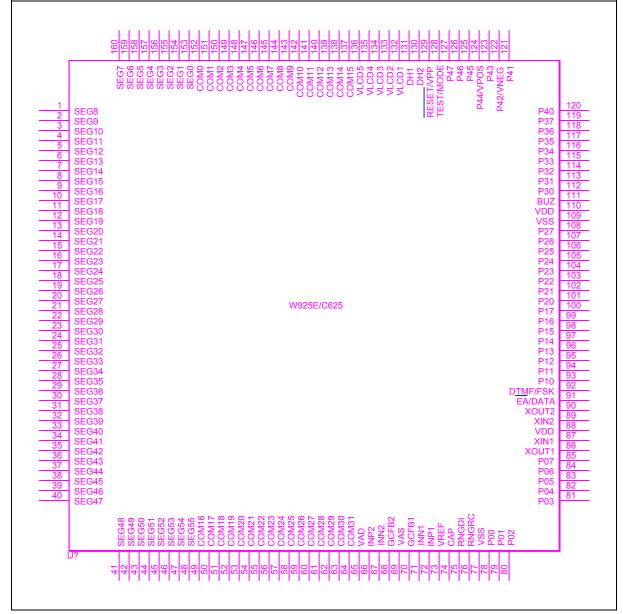

Figure 3-1 shows the pin assignment. The package type is 160pin QFP.

Figure 3-1 W925E/C625 Pin Configuration

### 4. PIN DESCRIPTION

| SYMBOL                 | I/O   | DESCRIPTION                                                                                                                                                                                                                                                                              |

|------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEST/MODE              | I/O   | TEST pin. In E version (EEPROM type), it works as a Mode pin to select programming mode. In C version (Mask type), this pin with internal pull-low resistor.                                                                                                                             |

| EA /DATA               | I,I/O | Set high for normal function. In E version, it works as Data pin. In C version, this pin with internal pull-high resistor.                                                                                                                                                               |

| RESET /V <sub>PP</sub> | I     | RESET pin. A low pulse causes the whole chip reset. In E version, this pin work as $V_{PP}$ pin, which is a supply programming voltage. In C version, this pin with internal pull-high resistor.                                                                                         |

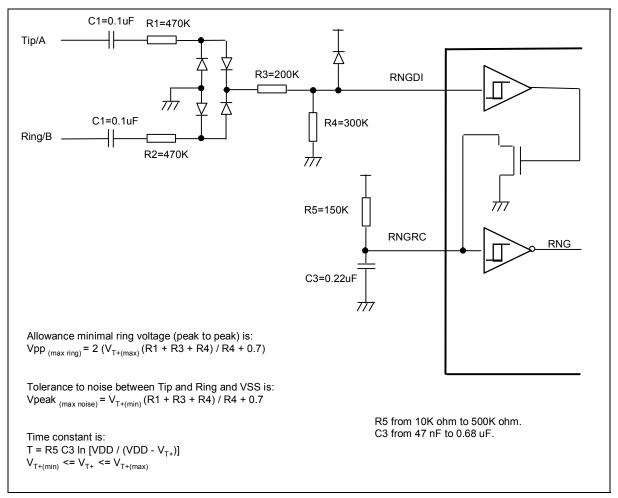

| RNGDI                  | I     | Ring Detect Input (Schmitt trigger input). Used for ring detection and line reversal detection. Must maintain a voltage between VAD and VAS.                                                                                                                                             |

| RNGRC                  | 0     | Ring RC (Open drain output and Schmitt trigger input). Used to set the time interval from the end of RNGDI pin to the inactive condition of the RNGON pin. An external resistor must connected to VAD and a capacitor connected to $V_{SS}$ , the time interval is the RC time constant. |

| CAP                    | 0     | Must be connected 0.1 $\mu$ F capacitor to V <sub>SS</sub> .                                                                                                                                                                                                                             |

| VREF                   | 0     | Reference Voltage. Nominally, $V_{\text{DD}}/2$ is used to bias the input of the gain control op-amp.                                                                                                                                                                                    |

| GCFB1                  | 0     | Op-amp1 Feed-back Gain Control signal. Select the input gain by connecting this pin and the INN1 pin with feedback resistor. It is recommended that the op-amp1 be set to unity gain.                                                                                                    |

| INN1                   | I     | Inverting Input of the gain control op-amp1.                                                                                                                                                                                                                                             |

| INP1                   | I     | Non-inverting Input of the gain control op-amp1.                                                                                                                                                                                                                                         |

| GCFB2                  | 0     | Op-amp2 Feed-back Gain Control signal. Select the input gain by connecting this pin and the INN2 pin with feedback resistor. It is recommended that the op-amp2 be set to unity gain.                                                                                                    |

| INN2                   | I     | Inverting Input of the gain control op-amp2.                                                                                                                                                                                                                                             |

| INP2                   | I     | Non-inverting Input of the gain control op-amp2.                                                                                                                                                                                                                                         |

| VAD                    | I     | Analog voltage supply.                                                                                                                                                                                                                                                                   |

| VAS                    | Ι     | Analog ground.                                                                                                                                                                                                                                                                           |

| V <sub>DD</sub>        | Ι     | Digital voltage supply.                                                                                                                                                                                                                                                                  |

| V <sub>SS</sub>        | Ι     | Digital ground.                                                                                                                                                                                                                                                                          |

| XOUT1                  | 0     | Output pin for main-oscillator. Connected to 3.58MHz crystal for CID function.                                                                                                                                                                                                           |

| XIN1                   | I     | Input pin for main-oscillator. Connected to 3.58MHz crystal for CID function.                                                                                                                                                                                                            |

| XOUT2                  | 0     | Output pin for sub-oscillator. Connected to 32.768KHz crystal only. Suggest to add an external capacitor about 10~30pF to ground (V <sub>SS</sub> ) for the accuracy of the oscillator.                                                                                                  |

Pin Description, continued

| SYMBOL         | I/O | DESCRIPTION                                                                                                                                                                                              |

|----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XIN2           | Ι   | Input pin for sub-oscillator. Connected to 32.768KHz crystal only. Suggest to add an external capacitor about 10~30Pf to ground ( $V_{SS}$ ) for the accuracy of the oscillator.                         |

| DTMF/FSK       | 0   | FTE=0, Dual-Tone Multi-Frequency(DTMF) signal output<br>FTE=1, FSK signal output                                                                                                                         |

| BUZ            | 0   | Buzzer output pin. If buzzer function is disabled, BUZ pin is in floating state.                                                                                                                         |

| P00-P07        | I/O | Input/Output port0. Port0 data can be bit controlled. The I/O mode is controlled by P0IO register. Port0 is open drain type when it is configured as output mode.                                        |

| P10-P17        | I/O | Input/Output port1 with pull high resistors. Port1 data can be bit controlled. The I/O mode is controlled by P1IO register. The P10-P13 and P14-P17 indicates the external interrupt pins(INT2 and INT3) |

| P20-P27        | I/O | Input/Output port2 with pull high resistors. Port2 data can be bit controlled. The I/O mode is controlled by P2IO register.                                                                              |

| P30-P37        | I/O | Input/Output port3 with pull high resistors. Port3 data can be bit controlled. The I/O mode is controlled by P3IO register. The special function of port3 is referred to the description of P3 register. |

| D40 D47        | I/O | Contents are byte controlled. Pull high and I/O mode can be bit controlled.                                                                                                                              |

| P40-P47        | 1/0 | The special function of P4 is referred to the description of P4 register.                                                                                                                                |

| VPOS,<br>VNEG  | I   | The comparator V+, V- analog input pins. Share pin with P4.2 and P4.4                                                                                                                                    |

| DH1,DH2        | Ι   | Connection terminals for LCD voltage doublers capacitor.                                                                                                                                                 |

| VLCD1-5        | I   | Positive LCD voltage supplies terminals.                                                                                                                                                                 |

| SEG0-<br>SEG55 | 0   | LCD segment output pins.                                                                                                                                                                                 |

| COM0-<br>COM31 | 0   | LCD common output pins.                                                                                                                                                                                  |

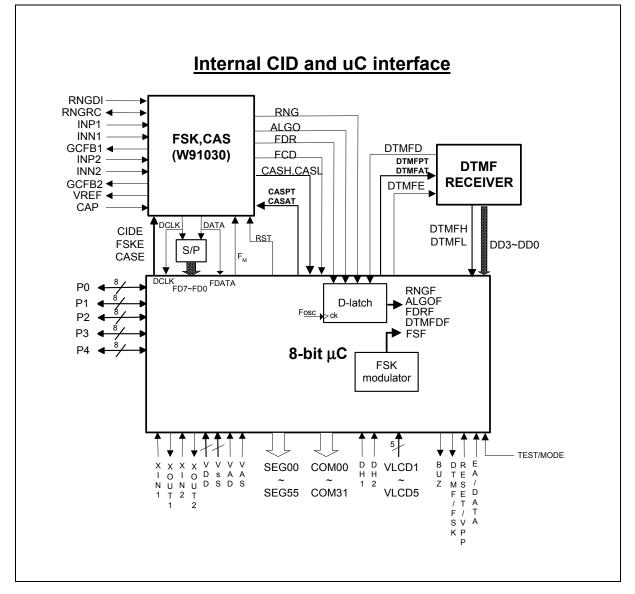

### 5. BLOCK DIAGRAM

### 6. FUNCTIONAL DESCRIPTION

The W925E/C625 is an 8-bit micro-controller with CID function. The 8-bit micro-control has the same instruction set as the 8051 family, with one addition: DEC DPTR (op-code A5H, the DPTR is decreased by 1). In addition, the W925E/C625 contains on-chip 4K + 224 bytes MOVX RAM.

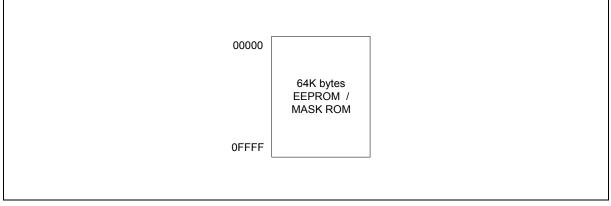

### ROM:

There are 64K bytes EEPROM/MASK ROM. The total 64K bytes EEPROM/MASK ROM is used for program code. The completely 64K bytes EEPROM/MASK ROM can be used for the look-up table memory.

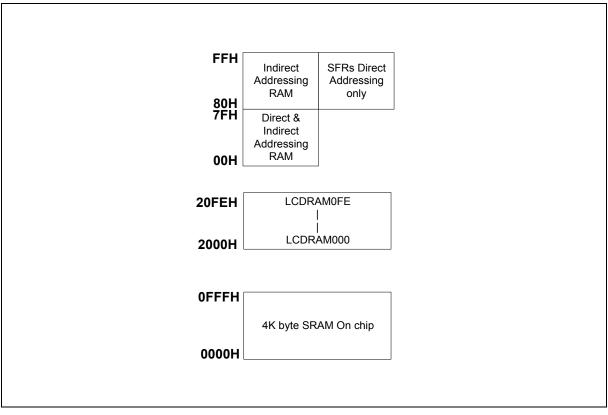

### On-chip Data RAM:

The W925E/C625 has 4K normal RAM + 224 Bytes of discontinuity LCD RAM which address is from 0000H to 0FFFH + 2000H to 20FEH. It only can be accessed by MOVX instruction; this on-chip RAM is optional under software control. The 224 bytes of RAM, which no appends to the 4K bytes RAM, are used for LCD RAM. The on-chip data RAM is not used for executable program memory. There is no conflict or overlap among the 256 bytes scratchpad RAM and the 4K Bytes MOVX RAM as they use different addressing modes and separate instructions.

### CID:

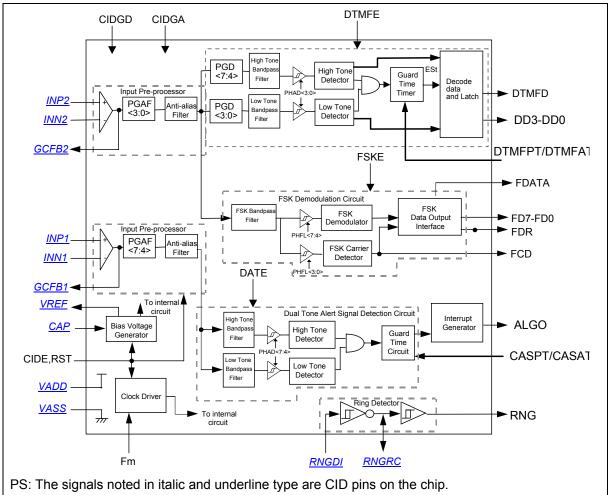

The CID functions include the FSK decoder, CAS detector, and DTMF decoder and ring detector.

### FSK modulator:

Support ITU-T V.23 and Bellcore 202 FSK transmit modulate signal

#### DTMF modulator:

The W925E/C625 built-in Dual tone multi-frequency generator.

#### I/O Ports:

The W925E/C625 has five 8-bit I/O ports giving 40 lines. Port0 to Port3 can be used as an 8-bit general I/O port with bit-addressable. The I/O mode of each port are controlled by PxIO registers. Port 1 to Port 4 have internal pull high resistors enabled/disabled by PxH registers. Port0 is open-drain type in output mode.

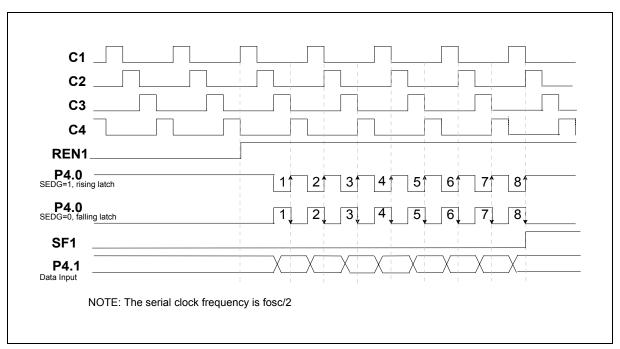

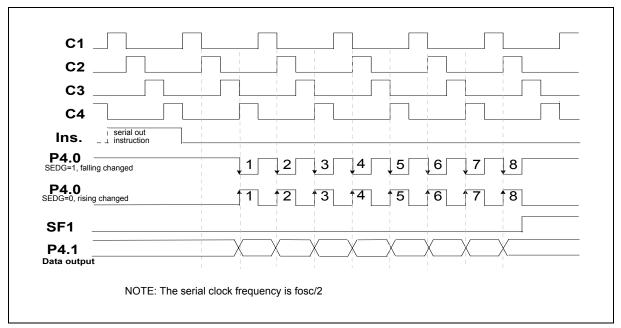

#### Serial I/O port:

The serial port, through P4.0 (SCLK) and P4.1 (SDATA), is an 8-bit synchronous serial I/O interface.

#### Timers:

The W925E/C625 has two 13/16-bit timers or 8 bits auto-reload timers. An independent watchdog timer is used as a System Monitor or as a very long time period timer. A divider can produce the divider interrupt in every period of 0.5S or 0.25S.

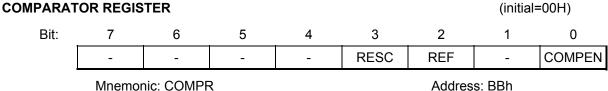

#### Comparator:

The W925E/C625 has an internal comparator with one external analog signal input path VNEG and an external path VPOS or a regulator voltage for the reference input REF1.

#### LCD:

The LCD display of 1792 dots is 1/5 bias with 56 segments and 32 commons. The LCD display of The LCD voltage is from internal regulator or external voltage source.

### Interrupts:

The W925E/C625 provides 11 interrupt resources with two priority level, including 4 external interrupt sources, 2 timer interrupts, 1 CID interrupt, 1 divider interrupt, 1 serial port interrupt, 1 comparator interrupt and 1 watchdog timer interrupt.

#### Power Management:

The W925E/C625 has IDLE and POWER DOWN modes of operation. In the IDLE mode, the clock to the CPU core is stopped however the functions of the timers, divider, CID and interrupts are active continuously. In the POWER DOWN mode, both of the system clock stop oscillating and the chip operation is completely stopped. POWER DOWN mode is the state of the lowest power consumption.

### 6.1 Memory Organization

The W925E/C625 separates the memory into two separate sections, the Program Memory and the Data Memory. The Program Memory is used to store the instruction op-codes and look-up table data, while the Data Memory is used to store data or for memory mapped devices.

### Program Memory:

The Program Memory on the W925E/C625 can be up to 64K bytes. The total 64K bytes EEPROM/MASK ROM are used to store the op-codes and the whole 64K can be used to store look-up table data.

Figure 6-1 Program Memory Map

### Data Memory:

The W925E/C625 contains on-chip 4K + 224 bytes MOVX RAM of Data Memory, which can only be accessed by MOVX instructions from the address 0000H to 0FFFH and from 2000H to 20FEH. In addition, the W925E/C625 has 256 bytes of on-chip scratchpad RAM. This can be accessed either by direct addressing or by indirect addressing. There are also Special Function Registers (SFRs), which can only be accessed by direct addressing. Since the scratchpad RAM is only 256 bytes, it can be used only when data contents are small. In the event that larger data contents are present, the only one selection is on-chip MOVX RAM. The on-chip MOVX RAM can only be accessed by a MOVX instruction. However, the on-chip RAM has the fastest access times. The memory map is shown Figure 6-2 and Figure 6-3 shows the scratchpad RAM/Register addressing.

Figure 6-2 Memory Map

| 80h        |          |          |          | Indirect | RAM      |          |          |          |               |

|------------|----------|----------|----------|----------|----------|----------|----------|----------|---------------|

| 7Fh        |          |          |          | Direct   | RAM      |          |          |          |               |

| 30h<br>2Fh | 7F       | 7E       | 7D       | 7C       | 7B       | 7.0      | 79       | 70       | ┤₄₋┐          |

| 2Eh        | 77       | 76       | 75       | 70       | 73       | 7A<br>72 | 79       | 78<br>70 |               |

| 2Dh        | 6F       | 6E       | 6D       | 6C       | 6B       | 6A       | 69       | 68       |               |

| 2Ch        | 67       | 66       | 65       | 64       | 63       | 62       | 61       | 60       | 1             |

| 2Bh        | 5F       | 5E       | 5D       | 5C       | 5B       | 5A       | 59       | 58       | 1             |

| 2Ah        | 57       | 56       | 55       | 54       | 53       | 52       | 51       | 50       | 1             |

| 29h        | 4F       | 4E       | 4D       | 4C       | 4B       | 4A       | 49       | 48       |               |

| 28h        | 47       | 46       | 45       | 44       | 43       | 42       | 41       | 40       | Bit Addressab |

| 27h        | 3F       | 3E       | 3D       | 3C       | 3B       | 3A       | 39       | 38       |               |

| 26h        | 37       | 36       | 35       | 34       | 33       | 32       | 31       | 30       | 20H-2FH       |

| 25h        | 2F       | 2E       | 2D       | 2C       | 2B       | 2A       | 29       | 28       | 4 1           |

| 24h        | 27       | 26       | 25       | 24       | 23       | 22       | 21       | 20       | 4             |

| 23h        | 1F       | 1E       | 1D       | 1C       | 1B       | 1A       | 19       | 18       | 4             |

| 22h<br>21h | 17       | 16       | 15       | 14       | 13       | 12       | 11       | 10       | 4             |

| 20h        | 0F<br>07 | 0E<br>06 | 0D<br>05 | 0C<br>04 | 0B<br>03 | 0A<br>02 | 09<br>01 | 08<br>00 |               |

| 1Fh        | 07       | 00       | 05       | •        |          | 02       | 01       | 00       | ┤◀ᢇ           |

| 18h        |          |          |          | Banl     | k 3      |          |          |          |               |

| 17h        |          |          |          |          |          |          |          |          | -             |

| 10h        |          |          |          | Banl     | k 2      |          |          |          |               |

| )Fh        |          |          |          | <b>D</b> |          |          |          |          | 1             |

| 08h        |          |          |          | Banl     | K 1      |          |          |          |               |

| 07h 🛛      |          |          |          | Banl     | < 0      |          |          |          |               |

| 00h        |          |          |          | Dani     | κU       |          |          |          |               |

Figure 6-3 Scratchpad RAM/Register Addressing

### 6.2 Special Function Registers

The W925E/C625 uses Special Function Registers (SFRs) to control and monitor peripherals and their Modes.

The SFRs reside in the register locations 80-FFh and accessed by direct addressing only. Some of the SFRs are bit addressable. This is very useful in cases where one wishes to modify a particular bit without changing the others. The SFRs that are bit addressable are those whose addresses end in 0 or 8. The list of SFRs is as follows. The table is condensed with eight locations per row. Empty locations indicate that there are no registers at these addresses. The content of reserved bits or registers is not guaranteed.

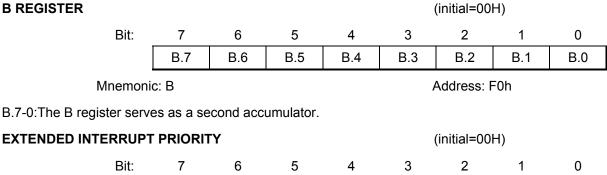

| F8 | EIP   | CIDGD | CIDGA |        |       |        |        |        |

|----|-------|-------|-------|--------|-------|--------|--------|--------|

| F0 | В     |       |       |        |       |        |        |        |

| E8 | EIE   |       |       |        |       |        |        |        |

| E0 | ACC   |       |       |        |       |        |        |        |

| D8 | WDCON |       |       |        |       |        |        |        |

| D0 | PSW   |       |       |        |       |        |        |        |

| C8 | DIVC  |       |       |        |       |        |        |        |

| C0 | SCON1 | SBUF1 | REGVC |        | PMR   | STATUS | FSKTC  | FSKTB  |

| B8 | IP    |       | DTMFG | COMPR  | IRC1  | IRC2   | CASPT  | CASAT  |

| В0 | P3    | CIDR  | CIDFG | CIDPCR | FSKDR | DTMFDR | DTMFPT | DTMFAT |

| A8 | IE    |       |       |        |       |        | P4IO   |        |

| A0 | P2    | HB    | P4H   |        |       |        | P4     |        |

| 98 |       |       |       | P1EF   |       | P1H    | P2H    | P3H    |

| 90 | P1    | EXIF  |       | P1SR   | P0IO  | P1IO   | P2IO   | P3IO   |

| 88 | TCON  | TMOD  | TL0   | TL1    | TH0   | TH1    | CKCON1 | CKCON2 |

| 80 | P0    | SP    | DPL   | DPH    | DPL1  | DPH1   | DPS    | PCON   |

### **Table 1 Special Function Register Location Table**

**Note:** The SFRs in the column with dark borders are bit-addressable.

Address: 84h

# W925E/C625

(initial=FFH,input mode)

A brief description of the SFRs now follows.

Mnemonic: DPL1

inbond

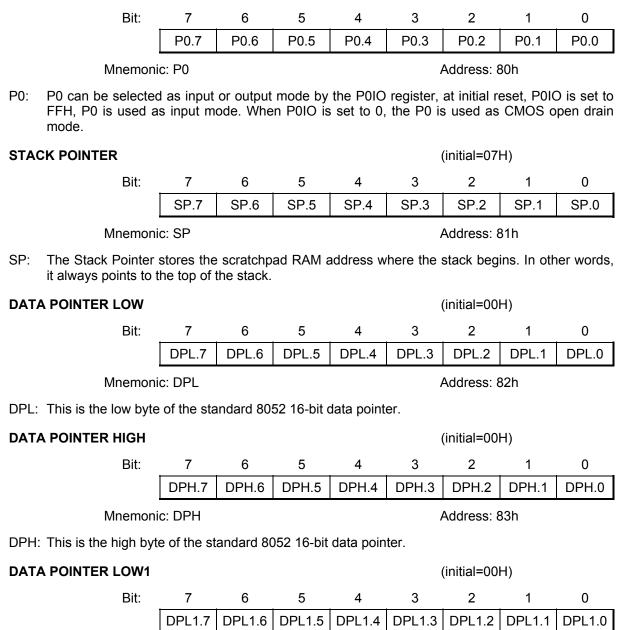

PORT 0

(initial=00H)

DPL1: This is the low byte of the new additional 16-bit data pointer. That has been added to the W925E/C625. The user can switch between DPL, DPH and DPL1, DPH1 simply by setting register DPS.0 = 1. The instructions that use DPTR will now access DPL1 and DPH1 in place of DPL and DPH. If they are not required, they can be used as conventional register locations by the user.

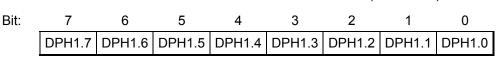

### DATA POINTER HIGH1

Mnemonic: DPH1

Address: 85h

DPH1: This is the high byte of the new additional 16-bit data pointer. That has been added to the W925E/C625. The user can switch between DPL, DPH and DPL1, DPH1 simply by setting register DPS = 1. The instructions that use DPTR will now access DPL1 and DPH1 in place of DPL and DPH. If they are not required, they can be used as conventional register locations by the user.

#### DATA POINTER SELECT

| (initial=00H) |  |

|---------------|--|

| <br>          |  |

Mnemonic: DPS

Address: 86h

(initial=00H)

- DPS.0: This bit is used to select either the DPL,DPH pair or the DPL1,DPH1 pair as the active Data Pointer. When set to 1, DPL1,DPH1 will be selected, otherwise DPL,DPH will be selected.

- DPS.1-7:These bits are reserved, but will read 0.

### **POWER CONTROL**

| Bit: | 7 | 6 | 5 | 4    | 3   | 2   | 1  | 0   |

|------|---|---|---|------|-----|-----|----|-----|

|      | - | - | - | IDLT | GF1 | GF0 | PD | IDL |

|      |   |   |   |      |     |     |    |     |

Mnemonic: PCON

Address: 87h

- IDLT: This bit controls the idle mode type. In idle mode when idle mode is released by any interrupt, if IDLT=1 it will not jump to the corresponding interrupt; if IDLT=0 it will jump to the corresponding interrupt.

- GF1-0: These two bits are general-purpose user flags.

- PD: Setting this bit causes the W925E/C625 to go into the POWER DOWN mode. In this mode, all the clocks are stopped and program execution is frozen. Power down mode can be released by INT0~INT3 and ring detection of CID interrupt.

- IDL: Setting this bit causes the W925E/C625 to go into the IDLE mode. The type of idle mode is selected by IDLT. In this mode the clocks to the CPU are stopped, so program execution is frozen. However, the clock path to the timers blocks and interrupt blocks is not stopped, and these blocks continue operating.

| TIMER CONTROL |     |     |     |     | (   | (initial=00 | H)  |     |

|---------------|-----|-----|-----|-----|-----|-------------|-----|-----|

| Bit:          | 7   | 6   | 5   | 4   | 3   | 2           | 1   | 0   |

|               | TF1 | TR1 | TF0 | TR0 | IE1 | IT1         | IE0 | IT0 |

|               |     |     |     |     |     |             |     |     |

Mnemonic: TCON

Address: 88h

- TF1: Timer 1 overflows flag. This bit is set when Timer 1 overflows. It is cleared automatically when the program does a timer 1 interrupt service routine. Software can also set or clear this bit.

- TR1: Timer 1 runs control. This bit is set or cleared by software to turn timer on or off.

- TF0: Timer 0 overflows flag. This bit is set when Timer 0 overflows. It is cleared automatically when the program does a timer 0 interrupt service routine. Software can also set or clear this bit.

- TR0: Timer 0 runs control. This bit is set or cleared by software to turn timer on or off.

- IE1: Interrupt 1 edge detect: Set by hardware when an edge/level is detected on INT1. This bit is cleared by hardware when the service routine is vectored to only if the interrupt was edge triggered. Otherwise, it follows the pin.

- IT1: Interrupt 1 type control: Set/cleared by software to specify falling edge/ low level triggered external inputs.

- IE0: Interrupt 0 edge detect: Set by hardware when an edge/level is detected on INT0. This bit is cleared by hardware when the service routine is vectored to only if the interrupt was edge triggered. Otherwise, it follows the pin.

- ITO: Interrupt 0 type control. Set/cleared by software to specify falling edge/ low level triggered external inputs.

#### TIMER MODE CONTROL

7 5 3 0 Bit: 6 4 2 1 GATE M1 M0 GATE M1 M0 C/T C/T

Mnemonic: TMOD

Address: 89h

(initial=00H)

Bit7~4 control timer 1, bit3~0 control timer0

- GATE: Gating control. When this bit is set, Timer x is enabled only while INTx pin is high and TRx control bit is set. When cleared, Timer x is enabled whenever TRx control bit is set.

- $C/\overline{T}$ : Timer or Counter Select. When cleared, the timer is incremented by internal clocks. When set, the timer counts high-to-low edges of the Tx pin.

Note: X is either 0 or 1.

M1, M0: Mode Select bits:

M1 M0 Mode

- 0 0 Mode 0: 13-bits timer

- 0 1 Mode 1: 16-bits timer

- 1 0 Mode 2: 8-bits with auto-reload from Thx

- 1 1 Reserved

| TIMER 0 LOW BYTE                    |                                                                                                                                                                                                                                                          |          | (initial=00 | H)    |           |             |       |       |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------|-------|-----------|-------------|-------|-------|

| Bit:                                | 7                                                                                                                                                                                                                                                        | 6        | 5           | 4     | 3         | 2           | 1     | 0     |

|                                     | TL0.7                                                                                                                                                                                                                                                    | TL0.6    | TL0.5       | TL0.4 | TL0.3     | TL0.2       | TL0.1 | TL0.0 |

| Mnemoni                             | ic: TL0                                                                                                                                                                                                                                                  |          |             |       | ŀ         | Address: 8  | BAh   |       |

| TL0.7-0: Timer 0 low byte           | e register.                                                                                                                                                                                                                                              |          |             |       |           |             |       |       |

| TIMER 1 LOW BYTE                    |                                                                                                                                                                                                                                                          |          |             |       | (         | (initial=00 | H)    |       |

| Bit:                                | 7                                                                                                                                                                                                                                                        | 6        | 5           | 4     | 3         | 2           | 1     | 0     |

|                                     | TL1.7                                                                                                                                                                                                                                                    | TL1.6    | TL1.5       | TL1.4 | TL1.3     | TL1.2       | TL1.1 | TL1.0 |

| Mnemoni                             | ic: TL1                                                                                                                                                                                                                                                  |          |             |       | ŀ         | Address: 8  | 3Bh   |       |

| TL1.7-0: Timer 1 low byte register. |                                                                                                                                                                                                                                                          |          |             |       |           |             |       |       |

| TIMER 0 HIGH BYTE (initial=00H)     |                                                                                                                                                                                                                                                          |          |             |       |           |             |       |       |

| Bit:                                | 7                                                                                                                                                                                                                                                        | 6        | 5           | 4     | 3         | 2           | 1     | 0     |

|                                     | TH0.7                                                                                                                                                                                                                                                    | TH0.6    | TH0.5       | TH0.4 | TH0.3     | TH0.2       | TH0.1 | TH0.0 |

| Mnemoni                             | c: TH0                                                                                                                                                                                                                                                   |          |             |       | ŀ         | Address: 8  | 3Ch   |       |

| TH0.7-0: Timer 0 high by            | te registe                                                                                                                                                                                                                                               | <i>.</i> |             |       |           |             |       |       |

| TIMER 1 HIGH BYTE                   |                                                                                                                                                                                                                                                          |          |             |       | (         | (initial=00 | H)    |       |

| Bit:                                | 7                                                                                                                                                                                                                                                        | 6        | 5           | 4     | 3         | 2           | 1     | 0     |

|                                     | TH1.7                                                                                                                                                                                                                                                    | TH1.6    | TH1.5       | TH1.4 | TH1.3     | TH1.2       | TH1.1 | TH1.0 |

| Mnemoni                             | c: TH1                                                                                                                                                                                                                                                   |          |             |       | ŀ         | Address: 8  | 3Dh   |       |

| TH1.7-0: Timer 1 high by            | te registe                                                                                                                                                                                                                                               | <b>.</b> |             |       |           |             |       |       |

| CLOCK CONTROL1                      |                                                                                                                                                                                                                                                          |          |             |       |           | (initial=00 | H)    |       |

| Bit:                                | 7                                                                                                                                                                                                                                                        | 6        | 5           | 4     | 3         | 2           | 1     | 0     |

|                                     | WD1                                                                                                                                                                                                                                                      | WD0      | T1S1        | T1S0  | T0S1      | T0S0        | DIVS  | M/S   |

| Mnemoni                             | ic: CKCO                                                                                                                                                                                                                                                 | N1       |             |       |           | Address: 8  | 3Eh   |       |

| timer. In all four t out period.    | Mnemonic: CKCON1 Address: 8Eh<br>WD1-0: Watchdog timer mode select bits: These bits determine the time-out period for the watchdog<br>timer. In all four time-out options, the reset time-out is 512 clocks more than the interrupt time-<br>out period. |          |             |       |           |             |       |       |

| WD                                  | )1 WD                                                                                                                                                                                                                                                    | 0 Inte   | errupt tim  | e-out | Reset tir | ne-out      |       |       |

| WD1 | WD0 | Interrupt time-out   | Reset time-out             |

|-----|-----|----------------------|----------------------------|

| 0   | 0   | Fosc/2 <sup>12</sup> | Fosc/2 <sup>12</sup> + 512 |

| 0   | 1   | Fosc/2 <sup>15</sup> | Fosc/2 <sup>15</sup> + 512 |

| 1   | 0   | Fosc/2 <sup>18</sup> | Fosc/2 <sup>18</sup> + 512 |

| 1   | 1   | Fosc/2 <sup>21</sup> | Fosc/2 <sup>21</sup> + 512 |

T0S0-1&T1S0-1: Timer0 & Timer1 clock source mode select bits. These bits determine the timer0 & timer1 clock source.

| T0S1<br>(T1S1) | T0S0<br>(T1S0) | Prescale clock<br>source |

|----------------|----------------|--------------------------|

| 0              | 0              | Fosc/2 <sup>2</sup>      |

| 0              | 1              | Fosc/2 <sup>6</sup>      |

| 1              | 0              | Fosc/2 <sup>10</sup>     |

| 1              | 1              | Fs                       |

|                |                |                          |

DIVS: Divider clock source control bit 1: DIVS = 0 :  $Fs/2^{13}$ DIVS = 1 :  $Fs/2^{14}$

M/S: System clock source control bit :

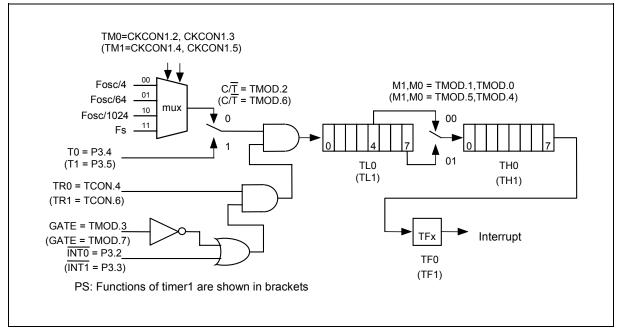

| CL | оск | CON | NTRO  | L2 |

|----|-----|-----|-------|----|

|    | 001 |     | 11110 |    |

$\overline{M}/S = 0$  : Fosc = XIN1 ( F<sub>M</sub>)  $\overline{M}/S = 1$  : Fosc = XIN2 ( Fs)

(initial=00H)

| Bit: | 7     | 6     | 5   | 4   | 3 | 2 | 1 | 0 |

|------|-------|-------|-----|-----|---|---|---|---|

|      | ENBUZ | BUZSL | KT1 | KT0 | - | - | - | - |

### Mnemonic: CKCON2

Address: 8Fh

ENBUZ: When ENBUZ=1 the BUZ pin works as buzzer output, otherwise BUZ pin is in floating state.

- BUZSL: Buzzer output selection. When BUZSL=0 BUZ is the output of octave tone. When BUZZL=1, BUZ is the output of key tone.

- KT1-0: Key tone frequency sources from divider. When divider is enable, KT1 and KT0 determines the key tone frequency.

| KT1 | KT0 | KEY TONE FREQUENCY |

|-----|-----|--------------------|

| 0   | 0   | Low                |

| 0   | 1   | 512Hz              |

| 1   | 0   | 1024Hz             |

| 1   | 1   | 2048Hz             |

| PORT 1 |             |      |      |      |      |      | (initial=FF | H,input m | ode) |

|--------|-------------|------|------|------|------|------|-------------|-----------|------|

|        | Bit:        | 7    | 6    | 5    | 4    | 3    | 2           | 1         | 0    |

|        |             | P1.7 | P1.6 | P1.5 | P1.4 | P1.3 | P1.2        | P1.1      | P1.0 |

|        | Mnemonic: F | Р1   |      |      |      |      | Address: 9  | 90h       |      |

P1.7-0: P1 can be selected as input or output mode by the P1IO register, at initial reset, P1IO is set to 1, so P1 is used as input mode. When P1IO is set to 0, the P1 is used as CMOS output mode. When P1EF are set and P1IO are set as input mode, P1 can be used as external interrupt source. The functions are listed below.

| P1.0 : INT2.0 External Interrupt 2<br>P1.1 : INT2.1 External Interrupt 2<br>P1.2 : INT2.2 External Interrupt 2<br>P1.3 : INT2.3 External Interrupt 2<br>P1.4 : INT3.0 External Interrupt 3<br>P1.5 : INT3.1 External Interrupt 3<br>P1.6 : INT3.2 External Interrupt 3<br>P1.7 : INT3.3 External Interrupt 3<br>(initial=00H) |                                   |            |             |             |             |             |          |        |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------|-------------|-------------|-------------|-------------|----------|--------|--|--|

| EXTERNAL INTERRUPT                                                                                                                                                                                                                                                                                                            | <b>FLAG</b>                       |            |             |             |             | (initial=00 | H)       |        |  |  |

| Bit:                                                                                                                                                                                                                                                                                                                          | 7                                 | 6          | 5           | 4           | 3           | 2           | 1        | 0      |  |  |

|                                                                                                                                                                                                                                                                                                                               | -                                 | -          | -           | COMPF       | DIVF        | CIDF        | IE3      | IE2    |  |  |

| Mnemonic: EXIF Address: 91h                                                                                                                                                                                                                                                                                                   |                                   |            |             |             |             |             |          |        |  |  |

| COMPF: Comparator flag. Set by hardware when RESC bit is from low to high.                                                                                                                                                                                                                                                    |                                   |            |             |             |             |             |          |        |  |  |

| DIVF: Divider overflows flag.                                                                                                                                                                                                                                                                                                 |                                   |            |             |             |             |             |          |        |  |  |

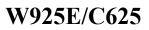

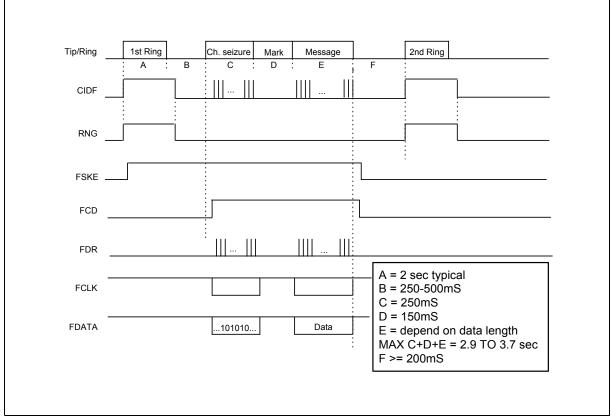

| CIDF: CID interrupts flag. Set by hardware when at least one of CID flags is set.                                                                                                                                                                                                                                             |                                   |            |             |             |             |             |          |        |  |  |

| IE3: External Interrupt                                                                                                                                                                                                                                                                                                       | -                                 | •          |             | -           | -           |             |          |        |  |  |

| IE2: External Interrupt                                                                                                                                                                                                                                                                                                       | 2 flag. Se                        | et by hard | ware whe    | n a falling | edge is d   | etected or  | n INT2.  |        |  |  |

| P1 PINS STATUS                                                                                                                                                                                                                                                                                                                |                                   |            |             |             |             | (initial=00 | H)       |        |  |  |

| Bit:                                                                                                                                                                                                                                                                                                                          | 7                                 | 6          | 5           | 4           | 3           | 2           | 1        | 0      |  |  |

|                                                                                                                                                                                                                                                                                                                               | P1.7SR                            | P1.6SR     | P1.5SR      | P1.4SR      | P1.3SR      | P1.2SR      | P1.1SR   | P1.0SR |  |  |

| Mnemoni                                                                                                                                                                                                                                                                                                                       | ic: P1SR                          |            |             |             |             | Address: 9  | 93h      |        |  |  |

| P1SR: Set when a falling                                                                                                                                                                                                                                                                                                      | g edge is o                       | detected c | on the corr | esponding   | g P1 pin, ( | clear by s  | oftware. |        |  |  |

| P0 I/O PORT CONTROL                                                                                                                                                                                                                                                                                                           |                                   |            |             |             |             | (initial=FF | H)       |        |  |  |

| Bit:                                                                                                                                                                                                                                                                                                                          | 7                                 | 6          | 5           | 4           | 3           | 2           | 1        | 0      |  |  |

|                                                                                                                                                                                                                                                                                                                               | P0.7IO                            | P0.6IO     | P0.5IO      | P0.4IO      | P0.3IO      | P0.2IO      | P0.1IO   | P0.0IO |  |  |

| Mnemoni                                                                                                                                                                                                                                                                                                                       | ic: P0IO                          |            |             |             |             | Address: §  | 94h      |        |  |  |

| P0IO: P0 pins I/O contro                                                                                                                                                                                                                                                                                                      |                                   |            |             |             |             |             |          |        |  |  |

| 1: input mode                                                                                                                                                                                                                                                                                                                 |                                   |            |             |             |             |             |          |        |  |  |

| 0: output mode                                                                                                                                                                                                                                                                                                                |                                   |            |             |             |             |             |          |        |  |  |

| P1 I/O PORT CONTROL                                                                                                                                                                                                                                                                                                           | P1 I/O PORT CONTROL (initial=FFH) |            |             |             |             |             |          |        |  |  |

| Bit:                                                                                                                                                                                                                                                                                                                          | 7                                 | 6          | 5           | 4           | 3           | 2           | 1        | 0      |  |  |

|                                                                                                                                                                                                                                                                                                                               | P1.7IO                            | P1.6IO     | P1.5IO      | P1.4IO      | P1.3IO      | P1.2IO      | P1.1IO   | P1.0IO |  |  |

| Mnemoni                                                                                                                                                                                                                                                                                                                       | ic: P1IO                          |            |             |             |             | Address: 9  | 95h      |        |  |  |

| P1I0:                                                         | P1 pins I/O contro<br>1: input mode<br>0: output mode | ol.        |                       |            |        |        |             |        |        |  |

|---------------------------------------------------------------|-------------------------------------------------------|------------|-----------------------|------------|--------|--------|-------------|--------|--------|--|

| P2 I/O                                                        | PORT CONTROL                                          |            |                       |            |        |        | (initial=FF | H)     |        |  |

|                                                               | Bit:                                                  | 7          | 6                     | 5          | 4      | 3      | 2           | 1      | 0      |  |

|                                                               |                                                       | P2.7IO     | P2.6IO                | P2.5IO     | P2.4IO | P2.3IO | P2.2IO      | P2.1IO | P2.0IO |  |

|                                                               | Mnemoni                                               | c: P2IO    |                       |            |        |        | Address: §  | 96h    |        |  |

| P2IO:                                                         | P2 pins I/O contro<br>1: input mode<br>0: output mode | ol.        |                       |            |        |        |             |        |        |  |

| P3 I/O PORT CONTROL (initial=FFH)                             |                                                       |            |                       |            |        |        |             |        |        |  |

|                                                               | Bit:                                                  | 7          | 6                     | 5          | 4      | 3      | 2           | 1      | 0      |  |

|                                                               |                                                       | P3.7IO     | P3.6IO                | P3.5IO     | P3.4IO | P3.3IO | P3.2IO      | P3.1IO | P3.0IO |  |

|                                                               | Mnemonic: P3IO Address: 97h                           |            |                       |            |        |        |             |        |        |  |

| P3IO: P3 pins I/O control.<br>1: input mode<br>0: output mode |                                                       |            |                       |            |        |        |             |        |        |  |

| P1 PIN                                                        | IS INTERRUPT EA                                       | BLE        |                       |            |        |        | (initial=00 | H)     |        |  |

|                                                               | Bit:                                                  | 7          | 6                     | 5          | 4      | 3      | 2           | 1      | 0      |  |

|                                                               |                                                       | P1.7EF     | P1.6EF                | P1.5EF     | P1.4EF | P1.3EF | P1.2EF      | P1.1EF | P1.0EF |  |

|                                                               | Mnemoni                                               | c: P1EF    |                       |            |        |        | Address: 9  | )Bh    |        |  |

| P1EF:                                                         | P1 pins interrupt 1<br>0: disable                     | function e | nabled/dis            | sabled reg | ister  |        |             |        |        |  |

|                                                               | 1: enable                                             |            |                       |            |        |        |             |        |        |  |

| P1 P                                                          | ULL-HIGH CONTR                                        | ROL        |                       |            |        |        | (initial=00 | H)     |        |  |

|                                                               | Bit:                                                  | 7          | 6                     | 5          | 4      | 3      | 2           | 1      | 0      |  |

|                                                               |                                                       | P1.7H      | P1.6H                 | P1.5H      | P1.4H  | P1.3H  | P1.2H       | P1.1H  | P1.0H  |  |

|                                                               | Mnemoni                                               | c: P1H     |                       |            |        | I      | Address: 9  | Dh     |        |  |

| P1H:                                                          | Port1 pins pull-hig<br>1: enable                      | gh resisto | <sup>-</sup> enable/d | isable     |        |        |             |        |        |  |

0: disable

| P2 P                            | PULL-HIGH CONT                                              | ROL          |              |            |            |          | (initial=00 | H)        |       |

|---------------------------------|-------------------------------------------------------------|--------------|--------------|------------|------------|----------|-------------|-----------|-------|

|                                 | Bit:                                                        | 7            | 6            | 5          | 4          | 3        | 2           | 1         | 0     |

|                                 |                                                             | P2.7H        | P2.6H        | P2.5H      | P2.4H      | P2.3H    | P2.2H       | P2.1H     | P2.0H |

|                                 | Mnemoni                                                     | c: P2H       |              |            |            |          | Address: 9  | 9Eh       |       |

| P2H:                            | Port1 pins pull-hi                                          | gh resisto   | r enable/d   | isable     |            |          |             |           |       |

|                                 | 1: enable                                                   |              |              |            |            |          |             |           |       |

|                                 | 0: disable                                                  |              |              |            |            |          |             |           |       |

| P3 P                            | ULL-HIGH CONT                                               | ROL          |              |            |            |          | (initial=00 | H)        |       |

|                                 | Bit:                                                        | 7            | 6            | 5          | 4          | 3        | 2           | 1         | 0     |

|                                 |                                                             | P3.7H        | P3.6H        | P3.5H      | P3.4H      | P3.3H    | P3.2H       | P3.1H     | P3.0H |

|                                 | Mnemon                                                      | c: P3H       |              |            |            |          | Address: §  | 9Fh       |       |

| P3H:                            | Port1 pins pull-hi                                          | gh resisto   | r enable/d   | isable     |            |          |             |           |       |

|                                 | 1: enable                                                   |              |              |            |            |          |             |           |       |

|                                 | 0: disable                                                  |              |              |            |            |          |             |           |       |

| PORT 2 (initial=FFH,input mode) |                                                             |              |              |            |            |          |             | ode)      |       |

|                                 | Bit:                                                        | 7            | 6            | 5          | 4          | 3        | 2           | 1         | 0     |

|                                 |                                                             | P2.7         | P2.6         | P2.5       | P2.4       | P2.3     | P2.2        | P2.1      | P2.0  |

|                                 | Mnemoni                                                     | c: P2        |              |            |            |          | Address: A  | \0h       |       |

| P2.7-0                          | ): Port 2 is an I/O p<br>by the P2IO regi<br>used as CMOS o | ster. At ini | itial reset, |            |            |          |             |           |       |

| HIGH                            | BYTE REGISTER                                               |              |              |            |            |          | (initial=00 | H)        |       |

|                                 | Bit:                                                        | 7            | 6            | 5          | 4          | 3        | 2           | 1         | 0     |

|                                 |                                                             | HB.7         | HB.6         | HB.5       | HB.4       | HB.3     | HB.2        | HB.1      | HB.0  |

|                                 | Mnemoni                                                     | c: HB        |              |            |            |          | Address: A  | A1h       |       |

| This re                         | egister contains the                                        | high byte    | address      | during exe | ecution of | " MOVX ( | @Ri, " inst | ructions. |       |

| P4 P                            | ULL-HIGH CONT                                               | ROL          |              |            |            |          | (initial=00 | H)        |       |

|                                 | Bit:                                                        | 7            | 6            | 5          | 4          | 3        | 2           | 1         | 0     |

|                                 |                                                             | P4.7H        | P4.6H        | P4.5H      | P4.4H      | P4.3H    | P4.2H       | P4.1H     | P4.0H |

|                                 | Mnemoni                                                     | c: P4H       |              |            |            |          | Address: A  | \2h       |       |

| P4H:                            | Port4 pins pull-hi                                          | gh resisto   | r enable/d   | lisable    |            |          |             |           |       |

|                                 | 1: enable                                                   |              |              |            |            |          |             |           |       |

|                                 | 0: disable                                                  |              |              |            |            |          |             |           |       |

| (∰ W | inbond            |

|------|-------------------|

|      | Electronics Corp. |

| PORT 4      |                              |              |             |            |          |           | (initial=FF | H input m | node)   |

|-------------|------------------------------|--------------|-------------|------------|----------|-----------|-------------|-----------|---------|

|             | Bit:                         | 7            | 6           | 5          | 4        | 3         | 2           | 1         | 0       |

|             | -                            | P4.7         | P4.6        | P4.5       | P4.4     | P4.3      | P4.2        | P4.1      | P4.0    |

|             | Mnemoni                      | c: P4        |             |            |          | 4         | Address: A  | A6h       | J       |

|             | e P4IO regis<br>is set to 00 | ster, at ini | tial reset, | P4IO is s  | et to 0F | Fh, P4 is | s used as   | input mo  | de. Whe |

| P4.4        | VPOS                         | Posit        | ive input o | of the com | parator  |           |             |           |         |

| P4.2        | VNEG                         | Nega         | ative input | of the co  | mparator |           |             |           |         |

| P4.1        | SDATA                        | Seria        | l port data | a I/O      |          |           |             |           |         |

| P4.0        | SCLK                         | Seria        | l port cloc | ck I/O     |          |           |             |           |         |

| INTERRUPT   | ENABLE                       |              |             |            |          |           | (initial=00 | H)        |         |

|             | Bit:                         | 7            | 6           | 5          | 4        | 3         | 2           | 1         | 0       |

|             |                              | EA           | ES1         | -          | -        | ET1       | EX1         | ET0       | EX0     |

|             | Mnemoni                      | c: IE        |             |            |          | ŀ         | Address: A  | A8h       |         |

| EA: Global  | enable. Ena                  | ble/disab    | e all inter | rupts.     |          |           |             |           |         |

| ES1: Enable | Serial port i                | interrupt    |             |            |          |           |             |           |         |

| ET1: Enable | Timer 1 inte                 | errupt       |             |            |          |           |             |           |         |

| EX1: Enable | external inte                | errupt 1     |             |            |          |           |             |           |         |

| ET0: Enable | Timer 0 inte                 | errupt       |             |            |          |           |             |           |         |

| EX0: Enable | external inte                | errupt 0     |             |            |          |           |             |           |         |

|             |                              |              |             |            |          |           | "           |           |         |

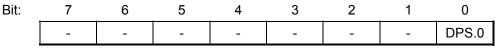

### P4 I/O PORT CONTROL

(initial=FFH)

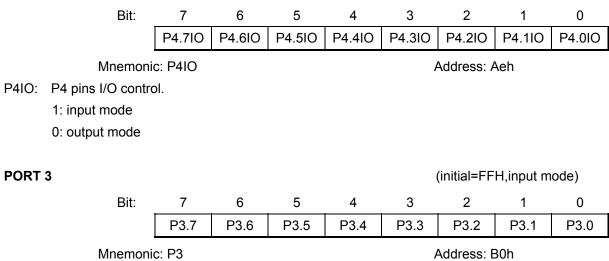

P3.7-0: P3 can be selected as input or output mode by the P3IO register, at initial reset, P3IO is set to 0FFH, P3 is used as input mode. When P3IO is set to 00h, the P3 is used as CMOS output mode. Special function of P3 is described below.

| P3.5 | T1          | Timer/Counter 1 external count input |

|------|-------------|--------------------------------------|

| P3.4 | Т0          | Timer/Counter 0 external count input |

| P3.3 | INT1        | External interrupt 1                 |

| P3.2 | <b>INTO</b> | External interrupt 0                 |

### CID REGISTER

(initial=00H,read only)

| Bit:    | 7       | 6    | 5     | 4   | 3     | 2         | 1    | 0   |

|---------|---------|------|-------|-----|-------|-----------|------|-----|

|         | -       | FCLK | FDATA | FCD | DTMFD | FDR       | ALGO | RNG |

| Mnemoni | c: CIDR |      |       |     | A     | ddress: E | 31h  |     |

This SFR indicates the CID signal immediately. Register data is set or cleared by hardware only.

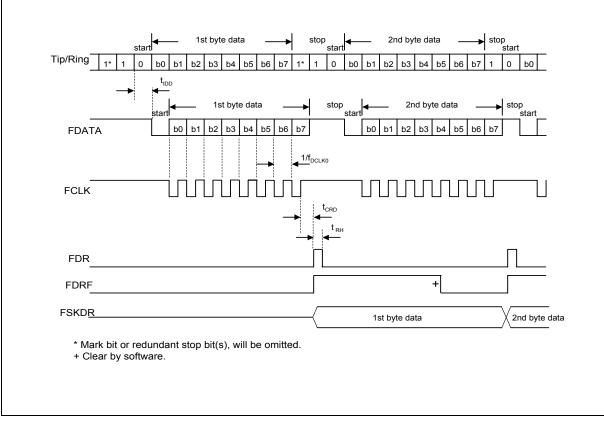

FCLK: FSK serial clock with the baud rate of 1200Hz.

FDATA: FSK serial bit data.

FCD: Set when FSK carrier is detected. Cleared when FSK carrier is disappeared.

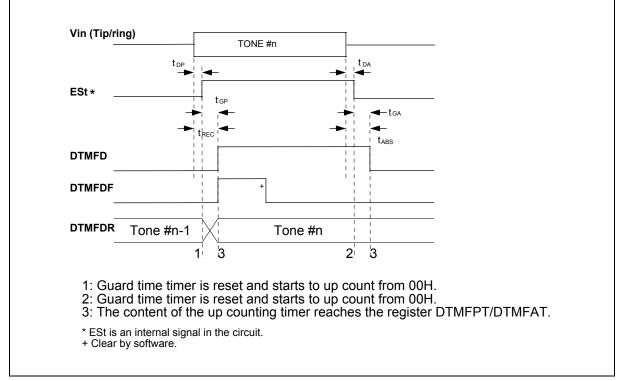

DTMFD: Set when DTMF decoded data is ready. Cleared when DTMF signal ends.

FDR: Set when FSK 8 bits data is ready. Cleared before next FSK start bit comes

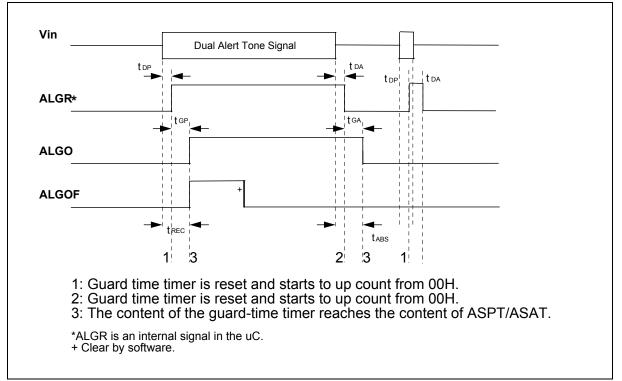

ALGO: Dual tone Alert signal Guard time detect signal. Set when a guard time qualified dual tone alert signal has been detected. Cleared when the guard time qualified dual tone alert signal is absent.

RNG: Ring detection bit. High to indicate the detection of line reversal and/or ringing.

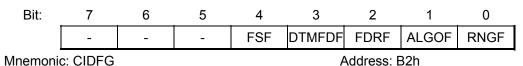

#### **CID FLAG GENERATOR**

(initial=00H)

FSF: Set when FSK Latch clock low to high. Cleared by software

DTMFDF: Set when DTMFD low to high. Cleared by software

FDRF: Set when FDR low to high. Cleared by software.

ALGOF: Set when ALGO low to high. Cleared by software.

RNGF: Set when RNG low to high. Cleared by software.

# inbond

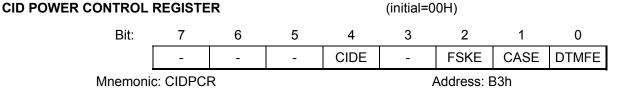

CIDE: Global enable CID function. Low to disable all functions of CID parts.

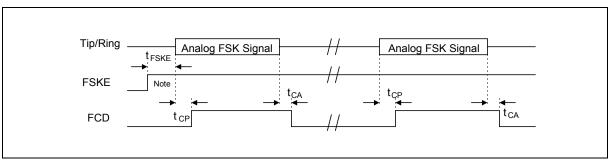

FSKE: Enable FSK demodulation circuit.

CASE: Enable Dual Tone Alert Signal detection circuit.

DTMFE: Enable DTMF demodulation circuit.

### **FSK DATA REGISTER**

| Bit:    | 7        | 6   | 5   | 4   | 3   | 2          | 1   | 0   |

|---------|----------|-----|-----|-----|-----|------------|-----|-----|

|         | FD7      | FD6 | FD5 | FD4 | FD3 | FD2        | FD1 | FD0 |

| Mnemoni | c: FSKDR |     |     |     | ļ   | Address: E | 34h |     |

(initial=XXH)

FD7-0: 8 bits FSK demodulated data.

### **DTMF DATA REGISTER**

| Bit:   | 7        | 6    | 5     | 4     | 3   | 2          | 1   | 0   |

|--------|----------|------|-------|-------|-----|------------|-----|-----|

|        | CASH     | CASL | DTMFH | DTMFL | DD3 | DD2        | DD1 | DD0 |

| nemoni | c: DTMFC | R    |       |       | ŀ   | Address: E | 35h |     |

Mnemonic: DTMFDR

CASH: Set when Dual Tone Alert Signal high tone is detected.

CASL: Set when Dual Tone Alert Signal low tone is detected.

- DTMFH: Set when DTMF high tone is detected.

- DTMFL: Set when DTMF low tone is detected.

- DD3-0: 4 bits DTMF demodulated data.

### DTMF PRESENT TIME REGISTER

|      |      |      |      |      |      | •         | ,    |      |

|------|------|------|------|------|------|-----------|------|------|

| Bit: | 7    | 6    | 5    | 4    | 3    | 2         | 1    | 0    |

|      | DPT7 | DPT6 | DPT5 | DPT4 | DPT3 | DPT2      | DPT1 | DPT0 |

| A    |      | T    |      |      |      | Adduces F |      |      |

Mnemonic: DTMFPT

Address: B6h

(initial=19H)

(initial=XXH)

The clock period of guard-time timer is 0.8582Ms. The default DTMF present time is 21.45Ms.

DPT7-0: The pre-set data register for counting DTMF present time. When DTMF is detected(Est low to high), the guard timer starts to up-count from 00H. As the guard timer is equal to the value of DTMFPT, the exist of the DTMF is accepted. Est changes to low state to stop and reset the counter.

| DTMF ABSENT TIME | REGISTER                   |   | (initial=19H) |     |   |   |   |

|------------------|----------------------------|---|---------------|-----|---|---|---|

| Bit:             | 7                          | 6 | 4             | 3   | 2 | 1 | 0 |

|                  | 5 DAT4 DAT3 DAT2 DAT1 DAT0 |   |               |     |   |   |   |

| Mnemo            |                            |   | Address: E    | 37h |   |   |   |

The clock period of guard-time timer is 0.8582Ms. The default DTMF absent time is 21.45Ms.

DAT7-0: The pre-set data register for counting DTMF absent time. When DTMF is absent(Est high to low), the guard timer starts to up-count from 00H. As the guard timer is equal to the value of DTMFAT, the finish of DTMF is recognized. Est changes to low state to stop and reset the counter.

### **INTERRUPT PRIORITY**

inbond

| Bit: | 7 | 6   | 5 | 4 | 3   | 2   | 1   | 0   |

|------|---|-----|---|---|-----|-----|-----|-----|

|      | - | PS1 | - | - | PT1 | PX1 | PT0 | PX0 |

Mnemonic: IP

Address: B8h

(initial=00H)

IP.7: This bit is un-implemented and will read high.

PS1: This bit defines the Serial port interrupt priority. PS1 = 1 sets it to higher priority level

PT1: This bit defines the Timer 1 interrupt priority. PT1 = 1 sets it to higher priority level.

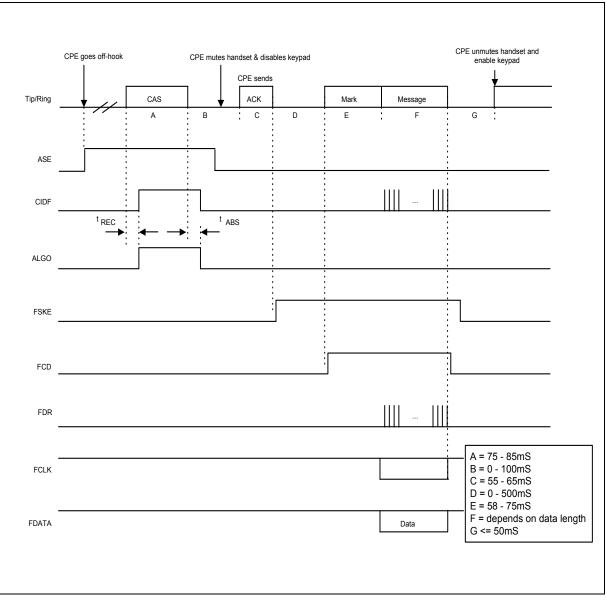

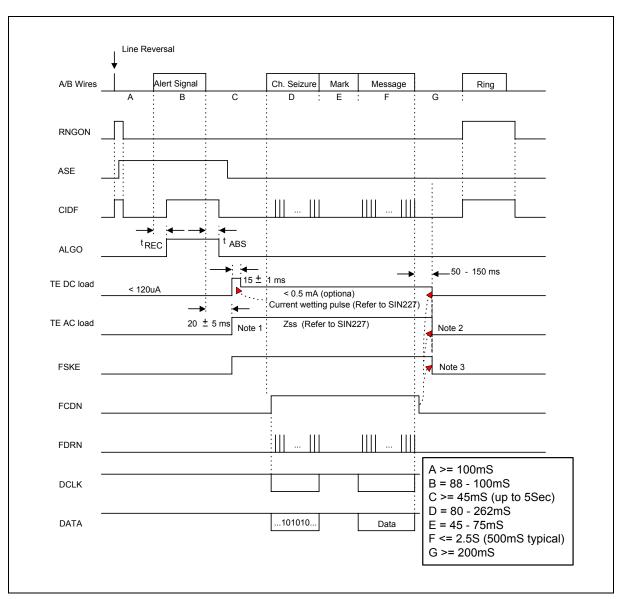

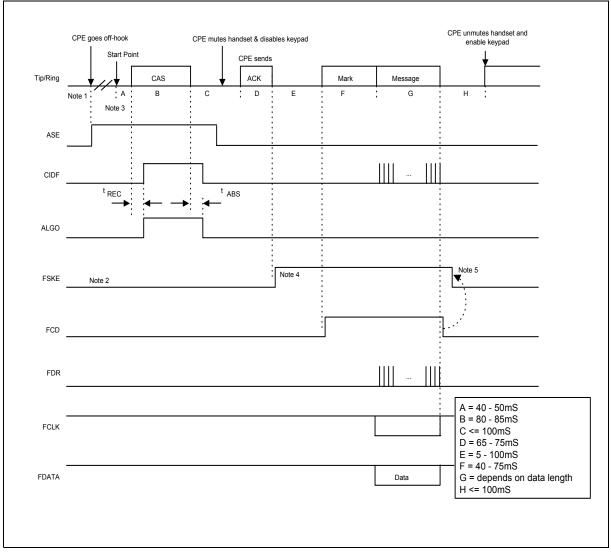

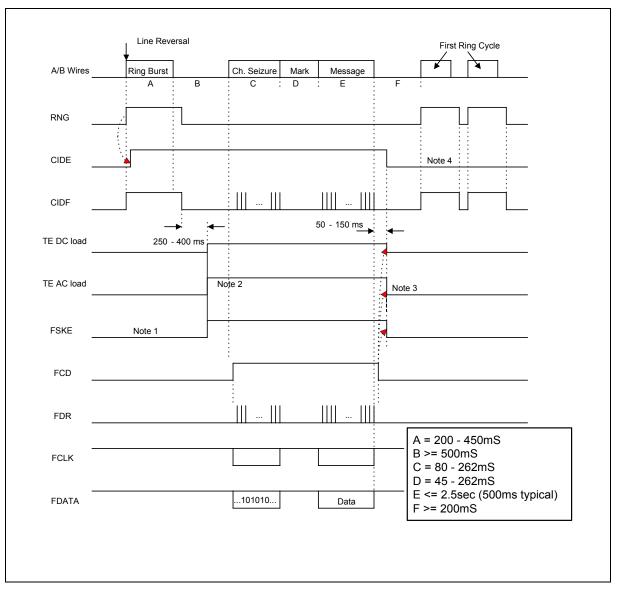

PX1: This bit defines the External interrupt 1 priority. PX1 = 1 sets it to higher priority level.